All the sessions from Transform 2021 are accessible on-demand now. Watch now.

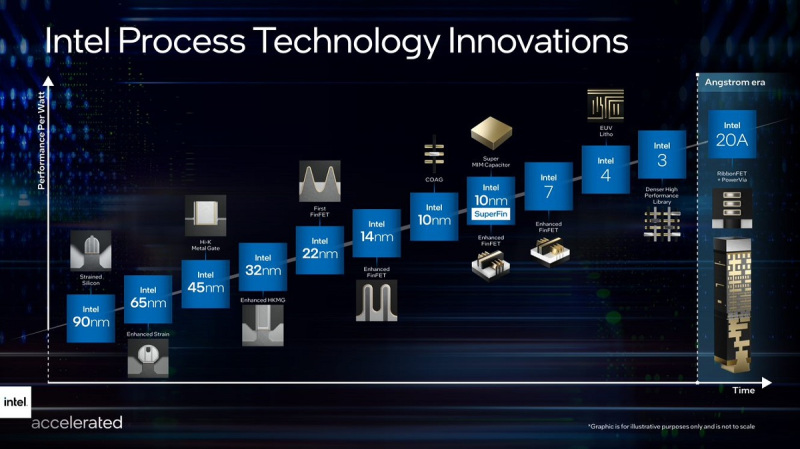

Under new management, Intel aims to recapture a crown that it owned for decades and regain technologies leadership in manufacturing chips by 2025.

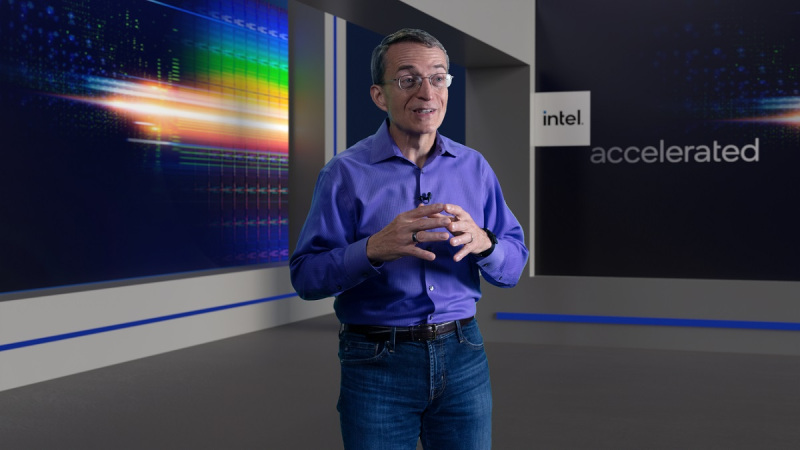

This will be difficult, as the organization has to invest tens of billions of dollars and get its technologies correct in the wake of various missteps, but new CEO Pat Gelsinger stated at an occasion that the large chipmaker is accelerating its investments in manufacturing processes and packaging innovations.

Intel’s news was one of the most detailed procedure and packaging technologies roadmaps the organization has ever supplied for its chip factories, and it showcased innovations that will energy goods by means of 2025 and beyond.

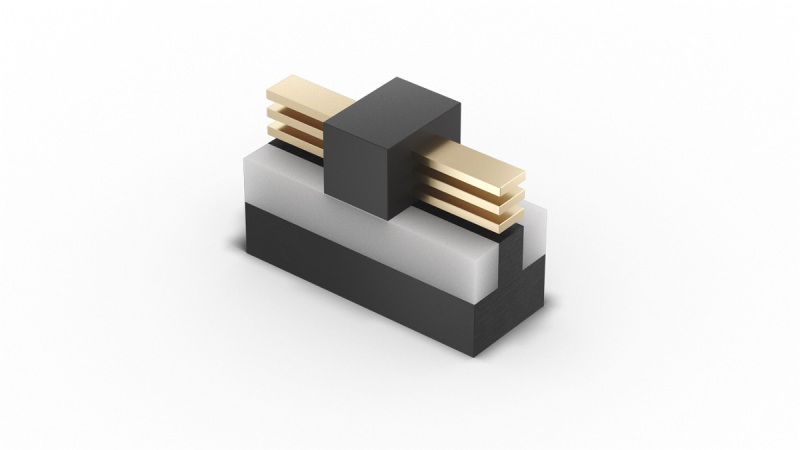

RibbonFET and PowerVia

Image Credit: Intel

In addition to announcing RibbonFET, its initially new transistor architecture in more than a decade, and PowerVia, an business-initially new backside energy delivery process, the organization highlighted its planned swift adoption of next-generation intense ultraviolet lithography (EUV), referred to as High Numerical Aperture (High NA) EUV.

Intel is positioned to get the initially High NA EUV production tool in the business.

“Building on Intel’s unquestioned leadership in advanced packaging, we are accelerating our innovation roadmap to ensure we are on a clear path to process performance leadership by 2025,” Gelsinger stated in the course of the worldwide Intel Accelerated webcast. “We are leveraging our unparalleled pipeline of innovation to deliver technology advances from the transistor up to the system level. Until the periodic table is exhausted, we will be relentless in our pursuit of Moore’s Law and our path to innovate with the magic of silicon.”

Santa Clara, California-based Intel described its roadmap of procedure and packaging innovations to energy the next wave of goods by means of 2025 and beyond. And Intel undoubtedly wants these innovations right after a couple of years of setbacks.

“Intel had some very significant missteps. But I think there’s sort of this prevailing view that the manufacturing folks at Intel aren’t doing anything right now,” stated David Kanter, an business analyst and president of Real World Insight, in an interview with VentureBeat. “It’s not like they went on vacation for three or four years. They’re trying to go where the future of technology is, and they’re putting those things into production. There’s a broad consensus that the next evolution in transistor architecture is what we need to drive performance.”

The organization also unveiled two “breakthrough” procedure technologies: RibbonFET, Intel’s initially new transistor architecture in more than a decade, and PowerVia, an business initially for backside energy delivery.

“The backside power delivery is more unique,” Kanter stated. “It’s an example of a technology that is actually really complicated to get work. And the main benefit is in terms of performance. It helps those customers. But there’s a broad swath of customers, where it’s not about performance, it’s about cost.”

Intel also stated it aims for continued leadership in sophisticated 3D packaging innovations with Foveros Omni and Foveros Direct technologies, which allow it to package chips in 3 dimensions.

Intel’s tactic has 3 legs. It is focusing on its factories for creating internal goods, like its microprocessors. It has Intel design and style groups that are design and style chips for external foundries. And it is investing heavily in factories that will make chips made by outdoors firms.

New node naming

Image Credit: Intel

One of the large alterations is in a category engineers usually refer to as “marketecture.” Intel is altering the way it names its manufacturing processes so it is each more aligned with the rest of the business and more correct when it comes to speaking about what type of chips can be made at every single stage of manufacturing.

“This is probably the most open disclosure of information that we’ve done in a very long time,” stated Sanjay Natarajan, common manager of Intel’s logic development group — an executive who came back right after Gelsinger became CEO this spring — in an interview with VentureBeat. “Pat talked before about how we do have an aspiration to be a leading provider of silicon globally.”

“We realized from a lot of people in the industry that our node naming is really not aligned with the rest of the industry,” he added. “Years ago, it used to represent a physical measurement on the transistor gate. It has long since stopped being a measurement of something specific there, and it’s more used as a label to describe technology. We’ve kind of realized that our naming has gotten confusing with the rest of the industry. Intel’s 10-nanometer was competitive with TSMC’s 7-nanometer and so on. Now we have a clear lexicon.”

Intel stated it is also preparing for the “angstrom era” of semiconductors, as it will turn to a new way of describing its manufacturing nodes in a couple of generations.

“Intel has been more honest than TSMC and Samsung on node naming. I think Intel’s renaming is fair and credible in the context of what TSMC and Samsung are doing,” stated Patrick Moorhead, an analyst at Moor Insights & Strategy, in an e-mail to VentureBeat. “There is no industry standard way yet to compare these nodes.”

The business has lengthy recognized that conventional nanometer-based procedure node naming stopped matching the actual gate-length metric in 1997. Today, Intel introduced a new naming structure for its procedure nodes, developing a clear and constant framework to give buyers a more correct view of procedure nodes across the business, Natarajan stated.

“I think Intel’s renaming is pretty consistent with the foundry naming scheme,” stated Kanter. “For historical reference, things got out of sync because of TSMC’s 16nm process, which was really their 20nm process with FinFET transistors. So it didn’t really improve density (but the FinFETs boosted performance), but TSMC decided to call it 16nm anyway … and the whole industry followed. I think a lot of the motivation here is adopting terminology that allows effective communication and understanding throughout the community of customers, suppliers, press, analysts, investors, etc. And generally, I think the renaming will help folks understand the situation more accurately.”

Intel stated the clarity is more critical than ever with the launch of Intel Foundry Services, which will manufacture chips made by other firms.

“The innovations unveiled today will not only enable Intel’s product roadmap; they will also be critical for our foundry customers,” Gelsinger stated. “The interest in IFS has been strong. IFS is off to the races.”

Intel 7, Intel 4, and Intel 3

Image Credit: Intel

Intel 7 seems to describe the equivalent of 7-nanometer manufacturing at rivals such as TSMC. Intel 7 delivers an about 10% to 15% functionality-per-watt raise versus the preceding generation, which was known as Intel 10-nanometer SuperFin, based on FinFET transistor optimizations.

Intel 7 will be featured in goods such as Alder Lake for consumers in 2021 and Sapphire Rapids for the datacenter, with the latter anticipated to be in production in the initially quarter of 2022.

Intel 4 totally embraces EUV lithography to print extremely little features making use of ultra-brief wavelength light. With an about 20% functionality-per-watt raise, along with location improvements, Intel 4 will be prepared for production in the second half of 2022 for goods shipping in 2023, which includes Meteor Lake for client and Granite Rapids for the datacenter.

“What they’re probably trying to communicate is a little denser than five, certainly not as dense as the next one,” Kanter stated. “I think it is reasonably accurate. One thing to keep in mind is that there’s a real divergence here in how area and power and performance are going to scale. And in that, I think Intel has set a bit more aggressive on performance than TSMC. And on density, it’s maybe a little less aggressive than TSMC.”

Intel 3 leverages additional FinFET optimizations and improved EUV to provide an 18% functionality-per-watt raise more than Intel 4, along with added location improvements. Intel 3 will be prepared to commence manufacturing goods in the second half of 2023.

The angstrom era

Image Credit: Intel

Intel 20A ushers in the angstrom era with two breakthrough technologies: RibbonFET and PowerVia. RibbonFET, Intel’s implementation of a gate-all-about transistor, will be the company’s initially new transistor architecture considering the fact that it pioneered FinFET in 2011.

The technologies delivers more quickly transistor switching speeds even though attaining the exact same drive present as many fins in a smaller sized footprint. PowerVia is Intel’s distinctive business-initially implementation of backside energy delivery, optimizing signal transmission by eliminating the have to have for energy routing on the front side of the wafer.

“Part of the reason we’re going to the term 20A is that we are bringing a few breakthrough innovations to light in this technology,” Natarajan stated. “One is our RibbonFET, which is a new transistor architecture. The other is PowerVia, which is a breakthrough interconnect innovation.”

Intel 20A is anticipated to ramp in 2024.

“We have a clear path to process leadership,” Natarajan stated. “In 2024, the Intel 20A node gets us to parity, and then Intel 18 gets us to leadership in 2025. Pat has put his foot on the gas for us, and this is an accelerated cadence of innovation.”

2025 and beyond

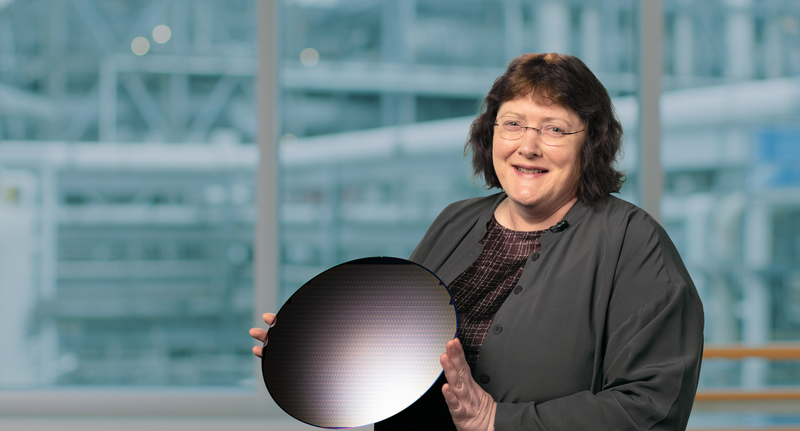

Image Credit: Intel

Beyond Intel 20A, Intel 18A is currently in development for early 2025, with refinements to RibbonFET that will provide a different main jump in transistor functionality. The organization is also working to define, develop, and deploy next-generation High NA EUV and expects to get the initially production tool in the business.

Intel is partnering closely with ASML to assure the achievement of this business breakthrough beyond the present generation of EUV.

“Intel has a long history of foundational process innovations that have propelled the industry forward by leaps and bounds,” stated Ann Kelleher, senior vice president and common manager of Technology Development, in the broadcast. “We led the transition to strained silicon at 90nm, to high-k metal gates at 45nm, and to FinFET at 22nm. Intel 20A will be another watershed moment in process technology with two groundbreaking innovations: RibbonFET and PowerVia.”

With Intel’s new IDM 2. tactic, the packaging is becoming even more critical to recognize the advantages of Moore’s Law.

Intel stated embedded multi-die interconnect bridge (EMIB) continues to lead the business as the initially 2.5D embedded bridge answer, with goods shipping considering the fact that 2017. Sapphire Rapids will be the initially Xeon datacenter solution to ship in volume with EMIB. It will also be the initially dual-reticle-sized device in the business, delivering practically the exact same functionality as a monolithic design and style. Beyond Sapphire Rapids, the next generation of EMIB will move from a 55-micron bump pitch to 45 microns.

On major of that, Foveros will leverage wafer-level packaging capabilities to provide a initially-of-its-type 3D stacking answer. Meteor Lake will be the second-generation implementation of Foveros in a client solution and features a bump pitch of 36 microns, tiles spanning many technologies nodes, and a thermal design and style energy variety from 5 watts to 125 watts.

Foveros Omni ushers in the next generation of Foveros technologies by promising flexibility with functionality 3D stacking technologies for die-to-die interconnect and modular styles. Foveros Omni permits die disaggregation, mixing many major die tiles with many base tiles across mixed fab nodes, and is anticipated to be prepared for volume manufacturing in 2023.

Foveros Direct moves to direct copper-to-copper bonding for low-resistance interconnects and blurs the boundary involving exactly where the wafer ends and the package starts. Foveros Direct enables sub-10 micron bump pitches delivering an order of magnitude raise in the interconnect density for 3D stacking, opening new ideas for functional die partitioning that had been previously unachievable. Foveros Direct is complementary to Foveros Omni and is also anticipated to be prepared in 2023.

The breakthroughs discussed today had been mainly created at Intel’s facilities in Oregon and Arizona, cementing the company’s part as the only top-edge player with each investigation and development and manufacturing in the U.S., Intel stated.

Additionally, the innovations draw on close collaboration with an ecosystem of partners in each the U.S. and Europe. Deep partnerships are essential to bringing foundational innovations from the lab to higher-volume manufacturing, and Intel is committed to partnering with governments to strengthen provide chains and drive financial and national safety.

The organization closed its webcast by confirming more particulars on its Intel InnovatiON occasion, which will be held in San Francisco and on-line October 27-28, 2021.

/cdn.vox-cdn.com/uploads/chorus_asset/file/25547838/YAKZA_3840_2160_A_Elogo.jpg)

/cdn.vox-cdn.com/uploads/chorus_asset/file/25547226/1242875577.jpg)

/cdn.vox-cdn.com/uploads/chorus_asset/file/25546751/ES601_WEBR_GalleryImages_KitchenCounterLineUp_2048x2048.jpg)