A new GamesBeat occasion is about the corner! Learn more about what comes next.

Intel has tens of thousands of chip designers, and they’ve been busy designing new chips that the laptop or computer chip giant hopes can bring it back into a leadership position.

Santa Clara, California-based Intel’s top rated chip architects — as nicely as CEO Pat Gelsinger — touted the styles at Intel Architecture Day 2021 in the hopes of instilling self-assurance in its leadership of the standard Computer computing platform, the x86 architecture. Intel has had a really hard time in the previous couple of years with each manufacturing delays and weaker styles compared to rival Advanced Micro Devices. Intel has lost market place share to AMD, and that is why Gelsinger was brought back to run the enterprise in February.

Now we’re in a position to see a peek at the unique central processing units (CPUs), graphics processing units (GPUs), and other chips that the enterprise has been designing in current years. One of the chip options, Ponte Vecchio, will have more than one hundred billion transistors, the on-off switches of digital technologies. All told, Intel had 14 unique architects and designers speak, beginning with Raja Koduri, a former AMD graphics executive and Intel’s senior vice president and basic manager of the Accelerated Computing Systems and Graphics Group.

Koduri showed off Intel’s initially overall performance hybrid architecture, code-named Alder Lake, with features that incorporated the intelligent Intel Thread Director for scheduling processing tasks. Intel also described Sapphire Rapids, the next-generation Intel Xeon Scalable processor for the datacenter. It also showed new infrastructure processing units and upcoming graphics architectures, like the Xe HPG and Xe HPC microarchitectures, and Alchemist and Ponte Vecchio method-on-chip computing options.

Webinar

Three top rated investment pros open up about what it requires to get your video game funded.

Watch On Demand

Image Credit: Intel

“Architecture is the alchemy of hardware and software,” stated Koduri in a press briefing. “It blends the best transistors for a given engine, connects them through advanced packaging, integrates high-bandwidth, low-power caches, and equips them with high-capacity, high-bandwidth memories and low-latency scalable interconnects for hybrid computing clusters in a package, while also ensuring that all software accelerates seamlessly. … The breakthroughs we disclosed today demonstrate how architecture will satisfy the crushing demand for more compute performance as workloads from the desktop to the data center become larger, more complex and more diverse than ever.”

Some analysts have been impressed with the occasion.

“The big takeaway for me was how comprehensive and far-reaching the architecture story was,” stated Bob O’Donnell, president of Technalysis Research, in an e mail to VentureBeat. “Another big point was how completely they have pivoted to multi-chip, multi-core designs. Whether it’s tiles or chiplets, it seems clear that the future of high-powered semis is clever packaging and combinations of different technologies into a bigger, more comprehensive design.”

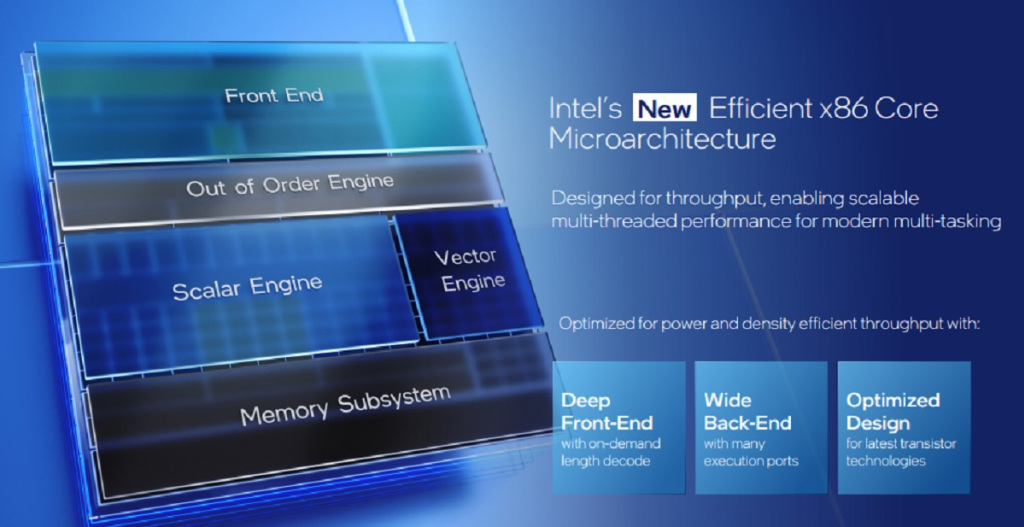

Efficient Core

Image Credit: Intel

One of the large projects, previously code-named Gracemont, went by the straightforward name of the Efficient Core. This chip family will have cores, or computing sub-brains, that are developed for energy efficiency. Four Efficient Cores on one chip will use 80% much less energy (than two predecessor Skylake cores operating 4 threads) and have 80% improved overall performance than the preceding generation, Koduri stated.

Compared with Skylake, Intel’s most prolific CPU microarchitecture, the Efficient-core delivers 40% more single-threaded overall performance at the identical energy, or the identical overall performance though consuming much less than 40% of the energy. A Skylake chip would have to consume 5 occasions more energy to provide the identical overall performance as an Efficient Core-based chip, stated Stephen Robinson, an Intel Fellow, in the press briefing.

Different chips in this family will differ based on the quantity of cores that are jammed into the bigger chip, which will be kept as compact as feasible for energy consumption and expense motives. This chip family can run at a low voltage to cut down general energy consumption though building the energy headroom to operate at larger frequencies. And it has improved approaches to predict how to procedure every single computing thread.

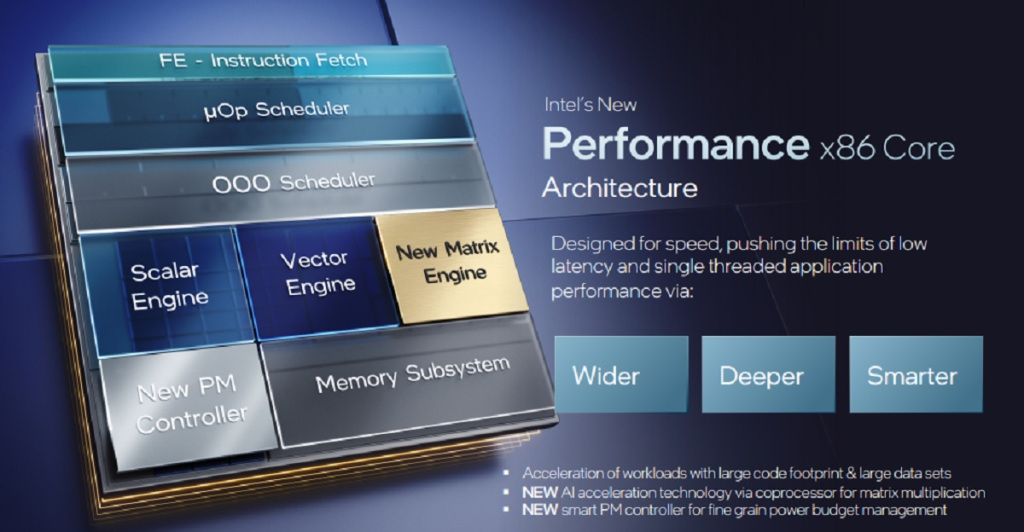

Performance Core

Image Credit: Intel

Intel’s new Performance Core microarchitecture, previously code-named Golden Cove, is developed for speed and pushes the limits of low latency and single-threaded application overall performance.

Workloads are developing in their code footprint and demand more execution capabilities. Datasets are also massively developing along with information bandwidth needs. Intel’s new Performance Core delivers a important increase in basic-objective overall performance and improved help for huge code footprint applications. It can do more items in parallel and more tasks in a provided time. It will be roughly 19% more quickly than 11th Gen Intel Core processors (dubbed Cypress Cove) at the moment on the market place.

It will also have Intel Advanced Matrix Extensions, the next-generation, constructed-in AI acceleration advancement, for deep mastering inference and coaching overall performance. It contains committed hardware and new instruction set architecture to execute matrix multiplication operations considerably more quickly than in the previous.

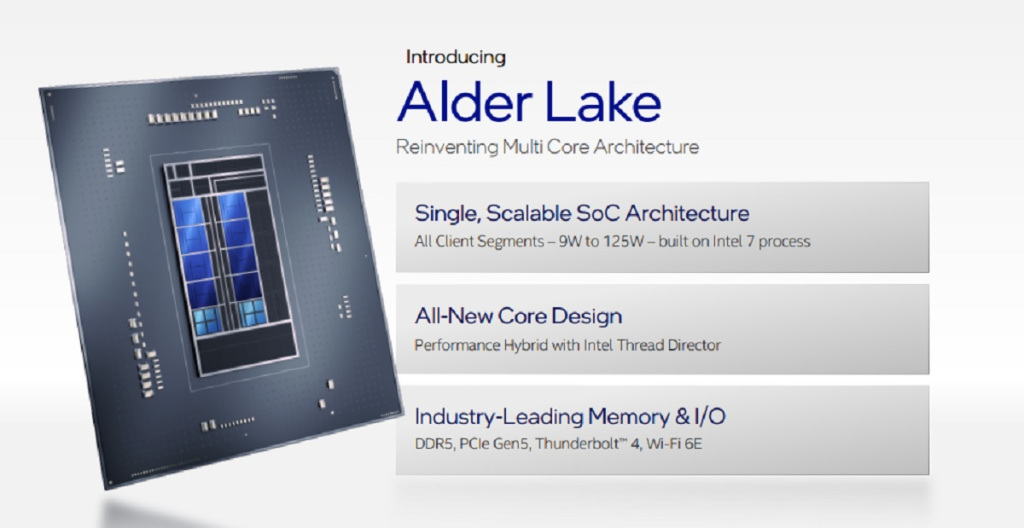

Alder Lake client chip

Image Credit: Intel

One of the new chips is Alder Lake, a client Computer processor that will combine each core sorts — Performance Core and Efficient Core — on a single chip. It will be constructed on the Intel 7 manufacturing procedure, which is equivalent to 7-nanometer chip production.

“I think that Intel will be very competitive with AMD on mobile form factors, especially on battery life with Alder Lake designs, but it remains to be seen what the total performance will be when you combine the 8 high-performance cores with the 8 efficiency cores and whether that will be competitive with AMD’s 12 Core or 10 Core offerings,” Sag stated. “Intel is claiming an average uplift of performance on the high-performance cores of 19%, which is considerable and could give them back the single-thread performance crown, but the final product when it gets into reviewers’ hands will ultimately determine that.”

To feed information into this processor, Intel has developed 3 independent fabrics, every single with actual-time, demand-based heuristics. The compute fabric can help up to 1,000 gigabytes per second (GBps), which is one hundred GBps per core or per cluster and connects the cores and graphics via the last level cache to the memory.

Intel Thread Director

In order for Performance Cores and Efficient Cores to work seamlessly with the operating method, Intel has created an enhanced scheduling technologies known as Intel Thread Director. Built straight into the hardware, Thread Director delivers low-level telemetry on the state of the core and the instruction mix of the thread. It empowers the operating method to spot the ideal thread on the ideal core at the ideal time. Thread Director is dynamic and adaptive – adjusting scheduling choices to actual-time compute desires – rather than a straightforward, static guidelines-based method. Intel is optimizing Thread Director for the greatest overall performance on Microsoft’s upcoming Windows 11 operating method.

Xe HPG Microarchitecture and Alchemist SoCs

Image Credit: Intel

Yes, Intel is acquiring back into the stand-alone graphics chip business enterprise in direct competitors with AMD and Nvidia for the initially time in quite a few years.

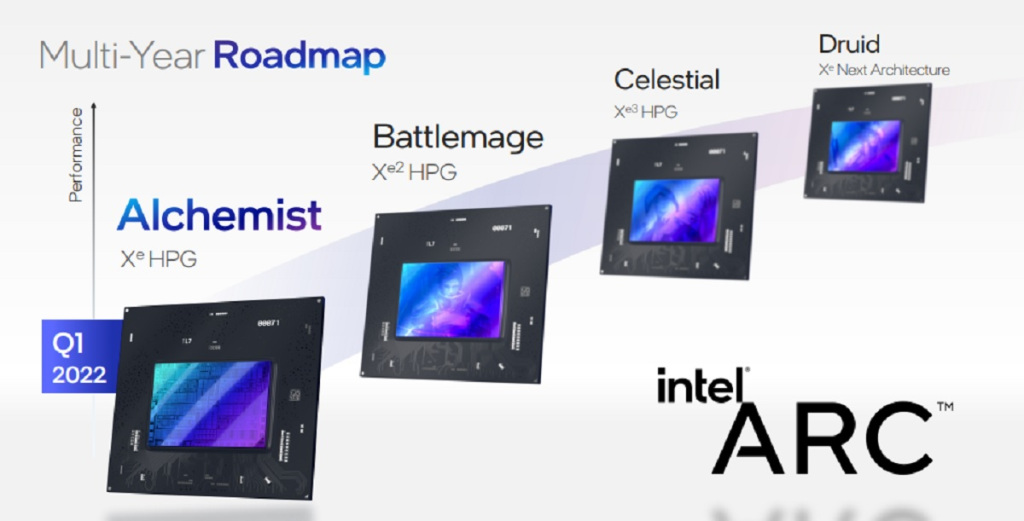

Xe HPG is a new discrete graphics microarchitecture developed to scale to enthusiast-class overall performance for gaming and creation workloads. The Xe HPG microarchitecture powers the Alchemist family of method-on-chips (SoCs), and the initially associated merchandise are coming to market place in the initially quarter of 2022 beneath the Intel Arc graphics chip brand. The Xe HPG microarchitecture features a new Xe-core, a compute-focused, programmable and scalable element. Three other graphics chips — Battlemage, Celestial, and Druid — will join Alchemist in coming years.

Taiwan’s TSMC will manufacture the Xe HPG on its N6 procedure node, which is quite uncommon for Intel. Intel also has a graphics enhancement dubbed XeSS, which utilizes deep mastering to synthesize photos in games that are close to the top quality of native higher-resolution rendering. Nvidia has a related technologies known as DLSS, and this tech will allow games that would only be playable at reduce top quality settings or reduce resolutions to run smoothly at larger top quality settings and resolutions.

“Xe HPG (Arc) is confirmed that it will be on a competitive TSMC N6 process node and appears to have all the features you would expect from a leadership graphics part. This could possibly help to alleviate some of the pressure on the GPU market,” stated Anshel Sag, senior analyst at Moor Insights & Strategy, in an e mail to VentureBeat.

Datacenter chips

Image Credit: Intel

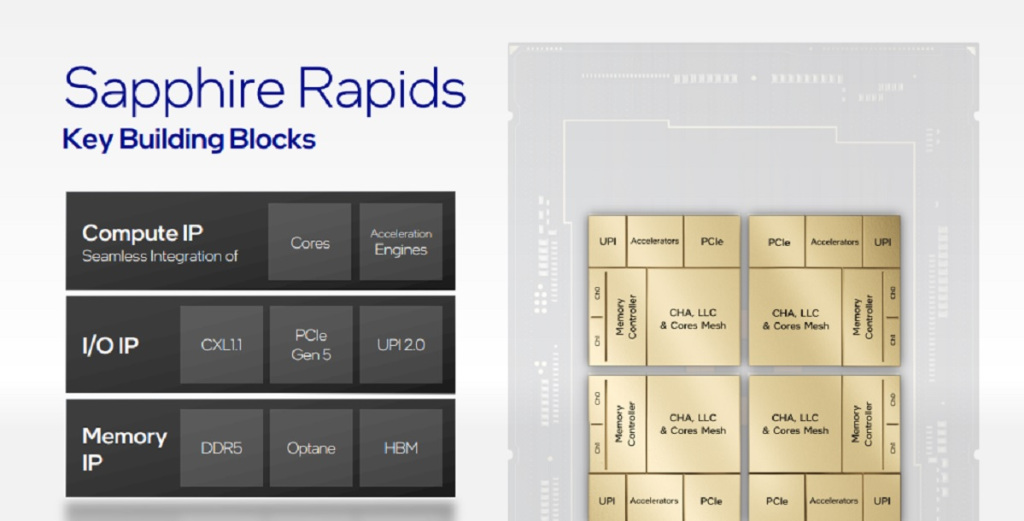

The next-generation Intel Xeon Scalable Processor (code-named Sapphire Rapids) is Intel’s large play in the datacenter chip market place.

The processor delivers substantial compute overall performance across dynamic and increasingly demanding information center usages and is workload-optimized to provide higher overall performance on elastic compute models like cloud, microservices, and AI. It has a tiled, modular SoC architecture that utilizes Intel’s capability to connect a bunch of packages in a single remedy.

Sapphire Rapids is constructed on Intel 7 procedure technologies and features Intel’s new Performance Core microarchitecture, which is developed for speed and pushes the limits of low-latency and single-threaded application overall performance. Some AI applications will be in a position to run seven occasions more quickly on Sapphire Rapids employing its new Intel AMX extensions.

Infrastructure Processing Unit

The IPU is a programmable networking device developed to allow cloud and communication service providers to cut down overhead and totally free up overall performance for CPUs. IPUs can offload tasks from the CPU, carrying out tasks like managing storage visitors, which reduces latency though effectively employing storage capacity by way of a diskless server architecture.

Mount Evans is Intel’s initially custom IPU. Mount Evans has been architected and created hand-in-hand with a top rated cloud service provider and integrates learnings from many generations of field programmable gate arrays (FPGA) SmartNICs.

“I would say the Mount Evans news is a big deal since we don’t yet know who the CSP partner is on the design, but the fact that Intel is going to ship an ARM Server part is going to make big news within the industry,” Sag stated.

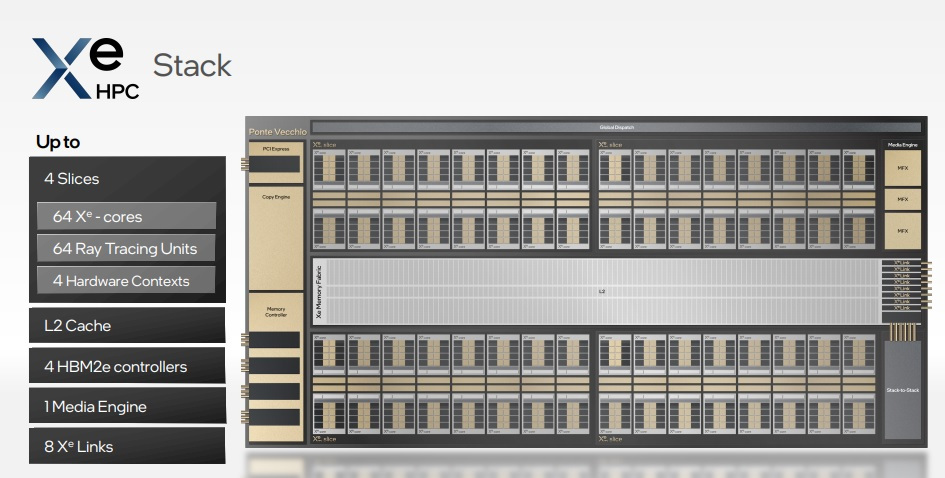

Ponte Vecchio

Image Credit: Intel

One of the most ambitious chips is Ponte Vecchio, which utilizes the graphics-focused Xe HPC microarchitecture. It requires all of the parallel processors and the many chips in a method to accelerate AI higher-overall performance computing and analytics workload applications. It aims to take Intel’s GPUs deep into the datacenter, Koduri stated.

Intel’s initially prototypes are operating at more than 45 teraflops (TFLOPS FP32) throughput, higher than 5 terabytes per second (TBps) memory fabric bandwidth and higher than 2 TBps connectivity bandwidth. Intel showed a demo displaying ResNet inference overall performance of more than 43,000 photos per second and higher than 3,400 photos per second with ResNet coaching for AI purposes. It will be constructed on TSMC’s sophisticated procedure technologies, dubbed N5.

“At a product specific-level, I think Ponte Vecchio will get the most attention, but I was impressed with what they’re doing with Thread Director on AlderLake,” O’Donnell stated. “I think that’s a practical, important step forward that a lot of PC users will be able to appreciate.”

Sag added, “The Ponte Vecchio part is also very interesting because of how complex it is (100 billion transistors) and how many challenges Intel had to overcome to make it possible. It appears to be going after NVIDIA’s A100 with not only a significant amount of Xe cores but also a significant amount of matrix cores which means that this is designed to be an AI powerhouse as well. The fact that it has a throughput of 45 TFLOPS FP32 is quite promising for the part, but will still boil down to software and developer outreach to enable that amount of computing.”

Intel’s foundry partnerships

Image Credit: Intel

While Intel is tapping one-time rival TSMC for its chip manufacturing, Intel is also arranging to make chips for other providers in Intel factories.

Stuart Pann, senior vice president in the corporate arranging group at Intel, stated that the company currently runs as a great deal as 20% of its

general solution volume at external foundries, or contract chip makers, and the enterprise is amongst the top rated buyers of TSMC. Some of that is due to acquisitions.

“We are evolving this integrated device manufacturer model to deepen and expand our partnerships with leading foundries,” Pann stated. “The reason is simple: Just as our designers use the right architecture for the right workload, we also choose the node that best fits that architecture. At this point in time, these foundry nodes are the right choice for our discrete graphics products.”

He noted that the upcoming Intel chip Meteor Lake for clientele will be made on the upcoming Intel 4 procedure technologies, with some supporting tiles manufactured at TSMC.

“Intel’s hybrid external/internal fab manufacturing approach is just what the company needs right now to regain its inside track, as it builds its IDM 2.0 future,” analyst Altavilla stated.

Summing it up

Image Credit: Intel

As pointed out, the analysts have been positive.

“I think the biggest news was the Alder Lake unveil, with a close second of Intel Alchemist Xe-HPG Graphics detail and XeSS,” stated Dave Altavilla, principal analyst at HotTech Vision And Analysis, in an e mail to VentureBeat. “I think they can be competitive versus AMD, as Alder Lake’s E-Core and P-Core architecture show good promise to scale across a myriad of workloads efficiently, and with much lower latency and input-output throughput versus the company’s previous generation.”

He added, “On the graphics front early signs of Alchemist are very strong, with Intel also checking all the right boxes supporting the full suite of DirectX Ultimate features set, with ray tracing and variable-rate shading, as well as an open-source and machine learning-accelerated super sampling alternative with XeSS. I think the market is going to wholeheartedly embrace a major third competitor and it’s going to be very interesting to watch versus AMD and Nvidia.”

Intel hopes these architectural breakthroughs will demonstrate how it can be a leader in the next generation of merchandise, Koduri stated. Intel didn’t describe the timing for when quite a few of the chips will arrive, with the exception of the graphics launch in early 2022.

“The breakthroughs we disclosed today also demonstrate how architecture will satisfy the crushing demand for more compute performance as workloads from the desktop to the data center become larger, more complex, and more diverse than ever,” Koduri stated.

He added, “Looking back at just the past year, technology was at the heart of how we all communicated, worked, played, and coped through the pandemic. Enormous computing power proved crucial. Looking ahead, we face a massive demand for compute – potentially a 1,000x need by 2025. That 1,000-times boost in four years is Moore’s Law to the power of five.”

Gelsinger, who is also a chip architect, closed the day saying, “We face daunting compute challenges that can only be solved through revolutionary architectures and platforms … Our talented architects and engineers made possible all this technology magic.”

He added, “Intel is back, and our story is just beginning.”

/cdn.vox-cdn.com/uploads/chorus_asset/file/22977156/acastro_211101_1777_meta_0002.jpg)